- Fecha: 2011.

- Propiedad y desarrollado por Cisium, Inc.

- Clientes: empresas industriales.

- Creadores: Raúl Bartolomé Castro y otros.

- Aporte de Raúl: jefe de proyecto, jefe de ingeniería y jefe de ingeniería. Adicionalmente, ingeniero senior de diseño electrónico y desarrollo de firmware.

- Mercado: industrial.

- Categoría de producto: automatización industrial.

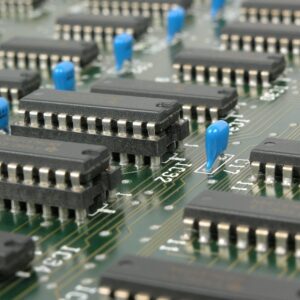

El alcance de este proyecto es una máquina industrial obsoleta y sin soporte del fabricante. La automatización del sistema se implementó con un tablero totalmente personalizado, utilizando componentes electrónicos discretos de naturaleza eléctrica analógica y digital. El objetivo era reparar las máquinas, sustituyendo los tableros dañados por un nuevo sistema de control.

Durante el análisis sistemático de la máquina y los casos de solución, decidimos rechazar la utilización de PLC estándar debido al espacio reducido para la ubicación de los componentes, además descartamos la posibilidad de hacer una pura ingeniería inversa (simplemente copiando el PCB) porque se basó en componentes obsoletos y de difícil acceso al mercado, finalmente decidimos crear un nuevo PCB desde cero utilizando la última tecnología, pero implementando el mismo comportamiento que la placa original.

El nuevo tablero de control fue diseñado alrededor del Xilinx CoolRunner-II CPLD XC2C64A, dando un nuevo aire al sistema permitiendo reprogramarlo en cualquier momento en lugar de una solución cableada. Ese fue el punto fuerte de la nueva solución: un sistema de reconfiguración fluido y sin ningún problema.

El CPLD se programó en VHDL utilizando una máquina de estados y conectividad de nivel esquemático al nivel superior. Gracias al software de diseño ISE WebPACK pudimos simular la máquina y crear un modelo preciso para el sistema que nos permite una fácil integración del programa.

Prestamos especial atención al diseño de las entradas, mantenemos el mismo margen de ruido en las entradas. Significa que, en lugar de crear entradas de 3,3 V, mantenemos el voltaje de suministro original de 12 V para las entradas para tener entradas robustas con respecto al ruido eléctrico. La implementación se realizó con comparadores usando histéresis y estableciendo el umbral de conmutación en 6V.

Características clave

Diseño basado en el CPLD Xilinx XC2C64A CoolRunner-II. Características:

- Optimizado para sistemas de 1,8 V

- Tan rápido como retrasos lógicos de pin a pin de 4,6 ns

- Corriente de reposo tan baja como 15 μA

- El mejor CPLD CMOS de 0,18 micras del sector

- Arquitectura optimizada para una síntesis lógica efectiva

- Operación de E/S multivoltaje: 1,5 V a 3,3 V

- Paquete VQFP de 44 pines con 33 E/S de usuario

- Funciones avanzadas del sistema

- El más rápido en programación de sistemas.

- ISP de 1,8 V que utiliza la interfaz IEEE 1532 (JTAG)

- Prueba de escaneo de límites IEEE1149.1 JTAG

- Entrada de disparador Schmitt opcional (por pin)

- Dos bancos de E/S separados

- Generación de términos de producto RealDigital 100% CMOS

- Opciones de señal global con control de macrocélula

- Múltiples relojes globales con selección de fase por macrocelda

- La salida global múltiple permite

- Configuración/reinicio global

- Relojes de términos de control eficientes, habilitaciones de salida y configuración/restablecimiento para cada macrocelda y compartidos entre bloques de funciones

- Seguridad de diseño avanzado

- Retención de bus opcional, 3 estados o pullup débil en pines de E/S seleccionados

- Opción de salida de drenaje abierto para unidad LED y OR con cable

- Tierras configurables opcionales en E/S no utilizadas

- Voltajes de E/S mixtos compatibles con niveles lógicos de 1,5 V, 1,8 V, 2,5 V y 3,3 V

- Arquitectura PLA

- Retención superior de pines

- Enrutabilidad del término del producto 100% a través del bloque de funciones

- Conectable en caliente

Todas las entradas con inmunidad al ruido de 5 V, histéresis de 1 V y filtrado de doble condensador, utilizando los comparadores cuádruples de bajo voltaje de compensación y baja potencia National Semiconductors LM2901. Características:

- Amplio rango de tensión de alimentación: 2 a 36 VCC o ±1 a ±18 VCC

- Consumo de corriente de suministro muy bajo (0,8 mA), independiente del voltaje de suministro

- Corriente de polarización de entrada baja: 25 nA

- Corriente de compensación de entrada baja: ±5 nA

- Tensión de compensación: ±3 mV

- El rango de voltaje de entrada en modo común incluye GND

- Rango de tensión de entrada diferencial igual a la tensión de alimentación

- Tensión de saturación de salida baja: 250 mV a 4 mA

- Voltaje de salida compatible con sistemas lógicos TTL, DTL, ECL, MOS y CMOS.

Las salidas las mejoramos utilizando los últimos transistores de potencia Darlington BDX53B de ON Semiconductor. Características:

- Alta ganancia de corriente CC − hFE = 2500 (típico) a IC = 4,0 Adc

- Tensión sostenida del emisor del colector − @ 100 mAdc

- VCEO(sat) = 2,0 VCC (máx.) @ IC = 3,0 Adc

- Bajo voltaje de saturación colector-emisor

- VCE(sat) = 2,0 Vcc (máx.) @ IC = 3,0 Adc

- VCE(sat) = 4,0 Vcc (máx.) @ IC = 5,0 Adc

- Construcción monolítica con resistencias en derivación de base-emisor incorporadas

- Paquetes sin Pb